# BRGF035012FWJ 2.5GHz~4GHz 12W Internal Matched PA

#### **Product Features**

Frequency: 2.5GHz ~ 4GHz Gain: 29.8dB@3.7GHz Psat: 41.9dBm@3.7GHz PAE: 50.4%@3.7GHz Operation Voltage: 28V,  $I_{DQ}$  130mA Package: QFN24(5mm×5mm)

#### **General Description**

The BRGF035012FWJ is a high-gain GaN internal matched power amplifier that achieves 12W saturated output in the 2.5GHz to 4GHz wide band with high power added efficiency (PAE=50.4%, Pout=42dBm@3.7GHz). In-band gain flatness up to  $\pm 0.5$ dB with a Pin of 21dBm. The product is ideal for pulse wave or carrier applications such as radar, public mobile radio communications and general purpose amplification modules.

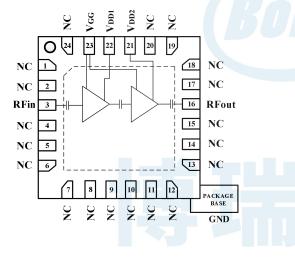

#### **Functional Block Diagram**

#### **Ordering Information**

| Part Number   | Package | Description                               |

|---------------|---------|-------------------------------------------|

| BRGF035012FWJ | QFN24   | 2.5GHz to 4GHz<br>12W Internal Matched PA |

| Æ             |         |                                           |

# 2.5GHz~4GHz 12W Internal Matched PA

#### **Absolute Maximum Ratings**

| Parameters                                          | Values |

|-----------------------------------------------------|--------|

| Gate Drain Breakdown Voltage<br>(BV <sub>DG</sub> ) | 100V   |

| Gate Voltage Range (V <sub>GG</sub> )               | -6~0V  |

| Gate Current (I <sub>G</sub> )                      | 4mA    |

| Channel Temperature (T <sub>CH</sub> )              | 275°C  |

| Mounting Temperature (30<br>seconds)                | 245°C  |

| Maximum Input Power                                 | 25dBm  |

Note:Operation of this device outside the parameter ranges given above may cause permanent damage. These are stress ratings only, and functional operation of the deviceat these conditions is not implied. Please pay attention to good heat dissipation under high temperature operation.

#### **Impedance Mismatch**

Test Conditions: DEMO board test, T<sub>A</sub> =25°C,

V<sub>DD</sub>=+28V, I<sub>DQ</sub>=130mA, Freq=3.3GHz, CW wave,

Pout=38dBm.

| Markers | Parameters                       | Тур. |

|---------|----------------------------------|------|

| VSWR    | Impedance Mismatch<br>Ruggedness | 10:1 |

#### **ESD WARNING**

## ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

#### **Recommended Operating Conditions**

| Parameters                              | Values       |

|-----------------------------------------|--------------|

| Drain Voltage (V <sub>DD</sub> )        | +28V (Typ)   |

| Drain Static Current (I <sub>DQ</sub> ) | 130mA (Typ)  |

| Gate Voltage (V <sub>GG</sub> )         | -2.81V (Typ) |

| Storage Temperature                     | -65°C~+150°C |

| Operating Temperature                   | -55°C~+85°C  |

Note: The electrical specifications of power amplifier tubes are tested under specified test conditions. Electrical performance is not guaranteed when the test specifications are exceeded.

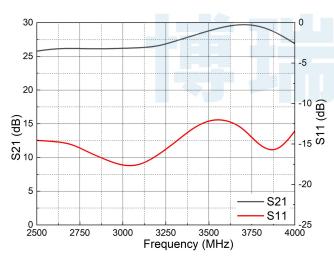

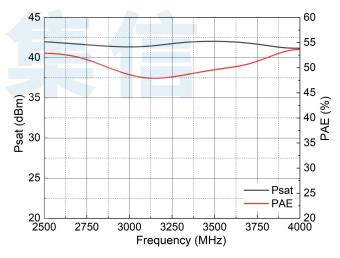

## Typical Performance (EVB test data,2.5GHz ~ 4GHz)

| Parameters                |       |       |       |       | Тур.  |       |       |       |       | Unit |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Frequency                 | 2500  | 2700  | 2900  | 3100  | 3300  | 3500  | 3700  | 3900  | 4000  | MHz  |

| Gain                      | 25.8  | 26.2  | 26.1  | 26.3  | 27.2  | 28.8  | 29.8  | 28.5  | 26.9  | dB   |

| Input Return Loss         | -14.5 | -14.9 | -16.9 | -17.7 | -14.9 | -12.0 | -13.0 | -16.1 | -13.4 | dB   |

| Output Return Loss        | -7.2  | -9.0  | -10.7 | -11.3 | -10.5 | -8.9  | -8.2  | -10.4 | -12.1 | dB   |

| Saturated Pout<br>( dBm ) | 42.0  | 41.7  | 41.4  | 41.3  | 42.0  | 42.1  | 41.9  | 41.2  | 41.2  | dBm  |

| PAE@P <sub>sat</sub>      | 52.9  | 52.5  | 49.6  | 47.5  | 48.4  | 49.8  | 50.4  | 53.4  | 53.7  | %    |

Test Condition: Temp =+25°C,  $V_{DD}$ =+28V,  $I_{DQ}$ =130mA; Psat&PAEwas pulse test, pulse width was 100us, duty cycle was 10%,  $I_{DQ}$  =6mA

Note: P<sub>sat</sub> defined as the saturation power output of the evaluation board.

#### **Typical Performance (EVB test results)**

Psat, PAE vs. Freq

<sup>(</sup>Pout=36dBm CW wave)

(Pout=36dBm CW wave)

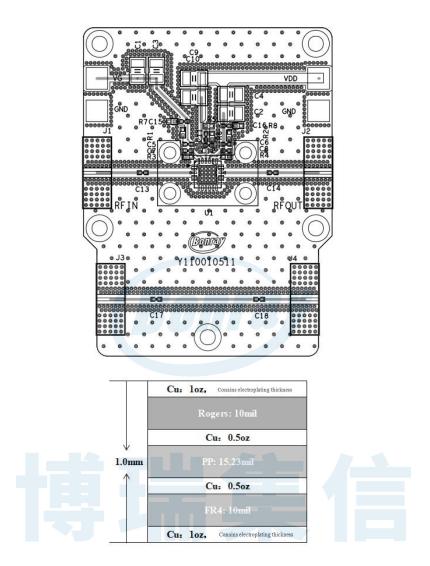

#### **PCB Evaluation Board**

Note: The C13 and C14 bit numbers actually use 0 ohm lines for short-circuitry processing, and it is recommended to replace the corresponding device with microstrip lines in PCB design.

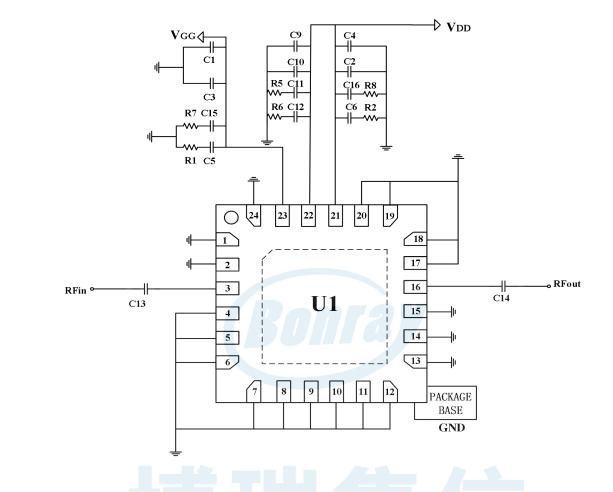

## **Typical Application Schematic**

#### **Bill of Material**

| Designator         | Description                             | Part Number          |

|--------------------|-----------------------------------------|----------------------|

| U1                 | 2.5GHz~4GHz 12W matched power amplifier | BRGF035012FWJ        |

| R1,R7              | 560 Ω                                   | RC0402JR-07560RL     |

| R2,R8,R5,R6        | 10 Ω                                    | RC0402JR-0710RL      |

| C5,C12,C6          | 1000pF                                  | C0402C102J1GACACAUTO |

| C11,C15,C16        | 100nF                                   | GRM155R71H104KE14D   |

| C1,C2,C3,C4,C9,C10 | 10uF                                    | GRM32EC72A106KE05#   |

| C13, C14           | 0 Ω                                     | /                    |

Note: \* indicates that the Designator is not used in the BOM of the corresponding frequency band. It is recommended to replace the corresponding bit number with a microstrip line during PCB design.

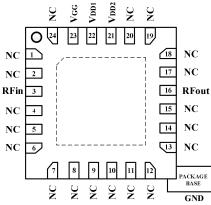

#### Pin Configuration and Description

| Pin Number                           | Pin Name         | Description                                                                                                                                                                   |

|--------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                                    | RFin             | Rf input, already internally matched to 50Ω;                                                                                                                                  |

| 16                                   | RFout            | Rf output, internally matched to 50Ω;                                                                                                                                         |

| 21                                   | V <sub>DD2</sub> | Secondary core drain Supply Voltage voltage                                                                                                                                   |

| 22                                   | V <sub>DD1</sub> | Primary core drain Supply Voltage voltage                                                                                                                                     |

| 23                                   | V <sub>GG</sub>  | The gate Supply Voltage voltage of the two-stage core                                                                                                                         |

| 4-trichlorobenzene 1 ~ 2 ~<br>20, 24 | NC               | The inside is not connected, and these ports need to be connected<br>to an external RF ground or DC ground when testing to achieve<br>RF isolation and good heat dissipation. |

| -                                    | ЕР               | Exposed pads, must be connected to RF ground and DC ground.                                                                                                                   |

#### **Power-on Sequence**

1. Set the gate voltage  $(V_{GG})$  to -5V

# Set the drain voltage (V<sub>DD</sub>) to +28V with a current limit of 1300mA

- 3. Turn on the gate voltage

- 4. Turn on drain voltage

- 5. Increase the gate voltage ( $V_{GG}$ ) so that the drain current is 130mA

- 6. Input RF signal

Note: In circuit design, bias voltage under-voltage protection is needed with timing protection circuits to ensure that  $V_{GG}$  is fully powered

up before  $V_{DD}$  is applied, and that  $V_{DD}$  is lowered to below 5V before  $V_{GG}$  is powered down, especially in  $T_{DD}$  applications. The gate

driving decoupling capacitor needs to be carefully evaluated to meet the switching speed requirements.

#### **Power-off Sequence**

- 1. Turn off the RF signal

- 2. Reduce the gate voltage  $(V_{GG})$  to -5V

- 3. Turn off the drain Supply Voltage voltage

- 4. Turn off the gate Supply Voltage voltage

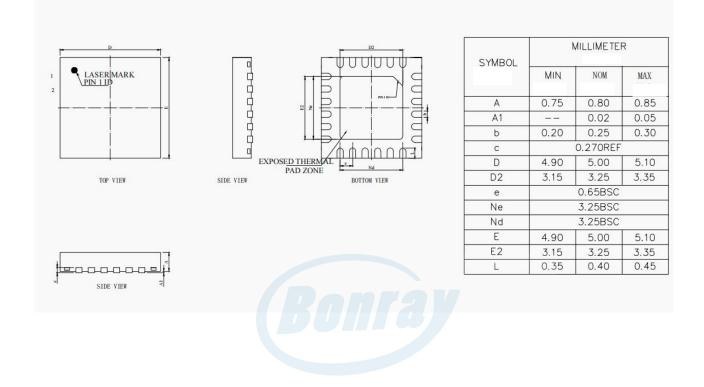

# Package Dimensions (mm)

V2.0.1