#### **Product Features**

Frequency: DC ~ 3.8GHz

Gain: 17.8dB@1.5GHz

Psat: 49.3dBm@1.5GHz

PAE: 53.6% (1.5GHz,Pout=49.3dBm)

Operation Voltage: 28V,  $I_{DO}$  500mA

Package: PC (ceramic seal)

## **General Description**

The BRGP038080PC is a pre-matched transistor designed using the GaN HEMT process, using a +28V drain supply to achieves 80W (49dBm) in the DC to 3.8GHz with a power added efficiency PEA (PAE) up to 50%. The advanced GaN HEMT process provides high efficiency, high gain and wide bandwidth. Its input terminal adopts pre-matching design, has good high frequency characteristics, reduces the sensitivity of external matching circuit, and is convenient for users to realize high frequency and ultra-wide band schemes through external matching design. The package form is a metal ceramic package with flange, excellent thermal conductivity, and the user can choose a variety of ways to install. This product is suitable for microwave communication, radar and other fields.

### **Application**

Power Amplification Stage for Wireless

Infrastructure

Test and Measurement Equipment

Commercial and Military Radars

Universal Transmitters and Jammers Ultrashort

wave Communication Equipment

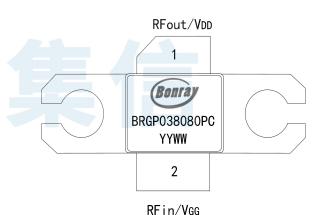

### **Functional Block Diagram**

## **Ordering Information**

| Part Number  | Package | Description                       |

|--------------|---------|-----------------------------------|

| BRGP038080PC | PC      | DC ~ 3.8GHz<br>80W GaN Transistor |

V2.0.2

web: www.bonray.net

tel: 0086+4006786538-810

## **Absolute Maximum Ratings**

| Parameters                                    | Values   |

|-----------------------------------------------|----------|

| Gate Drain Breakdown Voltage $(BV_{DG})$      | 100V     |

| Gate Voltage Range (V <sub>GG</sub> )         | -6 to 0V |

| Drain Current (I <sub>D</sub> )               | 7.5 A    |

| Gate Current (I <sub>G</sub> )                | 19mA     |

| Continuous Dissipated Power (P <sub>D</sub> ) | 86W      |

| Channel Temperature (T <sub>CH</sub> )        | 275 °C   |

| Mounting Temperature (30 seconds)             | 245 °C   |

Note:Operation of this device outside the parameter ranges given above may cause permanent damage. These are stress ratings only, and functional operation of the deviceat these conditions is not implied. Please pay attention to good heat dissipation under high temperature operation.

## **Recommended Operating Conditions**

| Parameters                                       | Values         |

|--------------------------------------------------|----------------|

| Drain Voltage (V <sub>DD</sub> )                 | +28V (Typ)     |

| Drain Static Current (I <sub>DQ</sub> )          | 500mA (Typ)    |

| Gate Voltage (V <sub>GG</sub> )                  | -2.61V (Typ)   |

| Channel Temperature (T <sub>CH</sub> )           | 225 ° C (Max)  |

| Continuous Dissipated Power CW (P <sub>D</sub> ) | 73W (Max)      |

| Storage Temperature                              | -65°C ~ +150°C |

| Operating Temperature                            | -55°C ~ +85°C  |

Note: The electrical specifications of power amplifier tubes are tested under specified test conditions. Electrical performance is not guaranteed when the test specifications are exceeded.

V2.0.2

web: www.bonray.net

# **Impedance Mismatch**

| Markers | Parameters         | Тур. |

|---------|--------------------|------|

| VSWR    | Impedance Mismatch | 5:1  |

| VSWIC   | Ruggedness         | 5.1  |

Test Conditions: DEMO board test, T<sub>A</sub> =25°C,

$V_{DD}$ =+28V,  $I_{DQ}$ =500mA, Fre=1GHz, CW,  $P_{out}$ =80W;

## **Thermal Parameters**

| rameters                              | <b>Test Conditions</b> | Value | Units |

|---------------------------------------|------------------------|-------|-------|

| Thermal resistance ()θ <sub>JC</sub>  | CW wave is tested      | 2.2   | °C/W  |

| Channel temperature ()T <sub>ch</sub> | at 70 ° C              | 225   | °C    |

Note:  $\theta_{JC}$  to measure the thermal resistance to the bottom of the package;

## **ESD WARNING**

ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

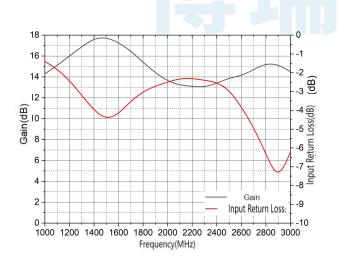

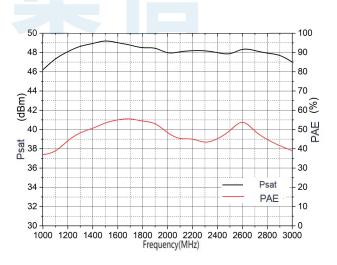

## **Typical Performance (Evaluation board data)**

|                                   | Evaluation Board (1.0GHz ~ 3.0GHz) Test Data |       |       |       |       |       |

|-----------------------------------|----------------------------------------------|-------|-------|-------|-------|-------|

| Parameters                        |                                              |       | Тур.  |       |       | Units |

| Frequency                         | 1000                                         | 1500  | 2000  | 2500  | 3000  | MHz   |

| Gain                              | 14.3                                         | 17.8  | 13.6  | 13.9  | 14.5  | dB    |

| Small Signal Input<br>Return Loss | -1.4                                         | -4.5  | -2.5  | -2.9  | -6.2  | dB    |

| Drain Current @P <sub>sat</sub>   | 3.566                                        | 5.487 | 4.065 | 3.833 | 4.082 | A     |

| Pout (dBm)@P <sub>sat</sub>       | 46.2                                         | 49.3  | 47.8  | 47.7  | 47.0  | dBm   |

| Pout (dBm)@P <sub>sat</sub>       | 41.6                                         | 86.0  | 60.9  | 58.8  | 49.7  | W     |

| PAE@P <sub>sat</sub>              | 36.9                                         | 53.6  | 48.0  | 49.0  | 39.0  | %     |

| Power Gain @P <sub>sat</sub>      | 9.47                                         | 13.77 | 9.91  | 9.78  | 9.87  | dB    |

Test Conditions: Temp =+25°C,  $V_{DD}$ =+28V,  $I_{DQ}$ =500mA, CW;

Note: P<sub>sat</sub> defined as the maximum power output by the evaluation board;

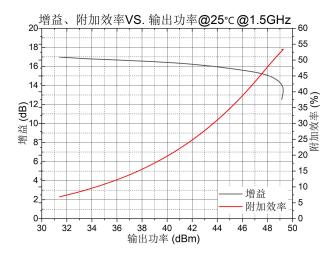

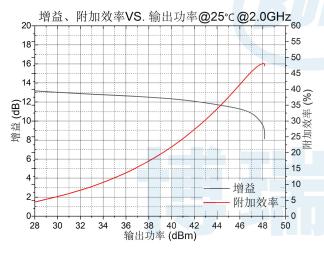

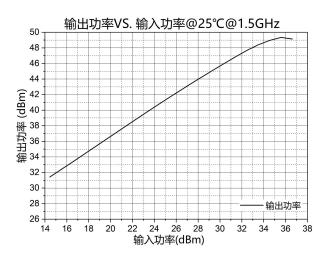

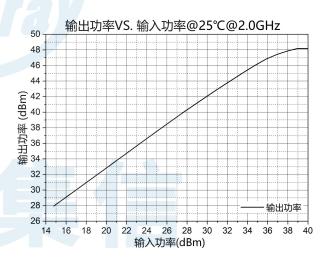

# Typical Performance(Evaluation board :1.0GHz-3.0GHz, Temp =+25°C, V<sub>DD</sub> =+28V, I<sub>DQ</sub> =500mA, CW wave test)

Psat,PEA vs. Freq @25℃

V2.0.2

web: www.bonray.net

tel: 0086+4006786538-810

Power Gain, PEA and output power curves (1.5GHz)

Power Gain, PEA and output power curve (2.0GHz)

output power and input power curves (1.5GHz)

output power and input power curve (2.0GHz)

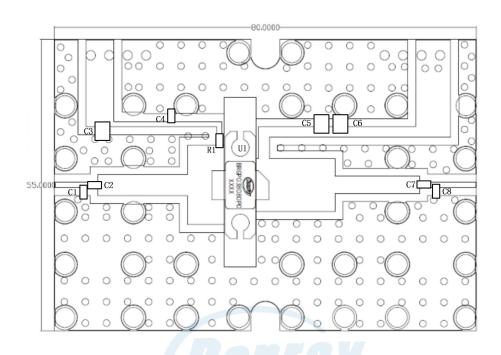

## **PCB Evaluation Board**

## **Bill of Material**

| Designator | Package | Description                | Part Number        |

|------------|---------|----------------------------|--------------------|

| U1         | PC      | 80W pre-matched transistor | BRGP038080PC       |

| C1         | 0603    | 0.5 pF                     | GRM1885C1HR60WA01  |

| C2,C4      | 0603    | 10pF                       | GRM1885C2A100JA01  |

| C7         | 0603    | 20PF                       | GQM1875C2E200FB12# |

| C8         | 0603    | 0.1 pF                     | GQM1875G2ER10BB12# |

| R1         | 0603    | 51 Ω                       | RC0603FR-0751R1L   |

| C3,C5,C6   | 1210    | 10uF                       | GRM32EC72A106KE05  |

V2.0.2

web: www.bonray.net

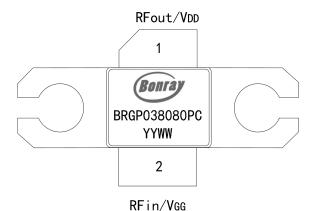

## Pin Configuration and Description

| Pin serial number | Pin name              | Description                                   |

|-------------------|-----------------------|-----------------------------------------------|

| 1                 | RFout/V <sub>DD</sub> | Drain voltage / RF Output matched to 50 ohms; |

| 2                 | RFin/V <sub>GG</sub>  | Gate voltage / RF Input matched to 50 ohms;   |

| -                 | Package Base          | Source connected to ground;                   |

### **Power-on Sequence**

- 1. Set the grid voltage  $(V_{GG})$  to -5V;

- 2. Set drain voltage (V<sub>DD</sub>) to +28V, current limit 10A;

- 3. Turn on the grid voltage;

- 4. Turn on drain voltage;

- 5. Increase the gate voltage  $(V_{GG})$  so that the drain current is 500mA;

- 6. Input RF signal;

# **Power-off Sequence**

- 1. Turn off the RF signal;

- 2. Reduce the grid voltage  $(V_{GG})$  to -5V;

- 3. Turn off the drain Supply Voltage voltage;

- 4. Turn off the grid Supply Voltage voltage;

Note: In circuit design, bias voltage under-voltage protection is needed with timing protection circuits to ensure that  $V_{GG}$  is fully powered up before  $V_{DD}$  is applied, and that  $V_{DD}$  is lowered to below 5V before  $V_{GG}$  is powered down, especially in  $T_{DD}$  applications. The gate driving decoupling capacitor needs to be carefully evaluated to meet the switching speed requirements.

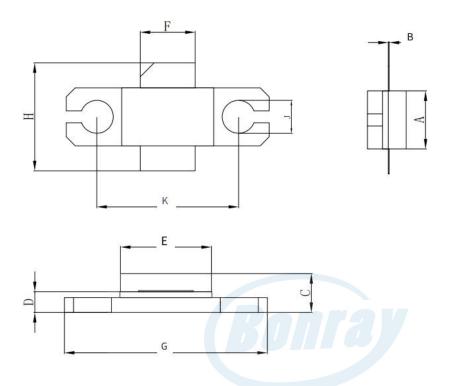

# **Package Dimensions (mm)**

| DTM. | Units man   |       |  |

|------|-------------|-------|--|

| DIM  | MIN         | MAX   |  |

| A    | 5, 67       | 5, 93 |  |

| В    | 0, 06       | 0, 15 |  |

| С    | 3, 18       | 4. 19 |  |

| D    | 1. 93       | 2.23  |  |

| E    | 9 9.2       |       |  |

| F    | 5, 37 5, 63 |       |  |

| G    | 20.17 20.43 |       |  |

| Н    | 10,3 11.3   |       |  |

| J    | 3.3±0.13    |       |  |

| K    | 14.2±0.13   |       |  |

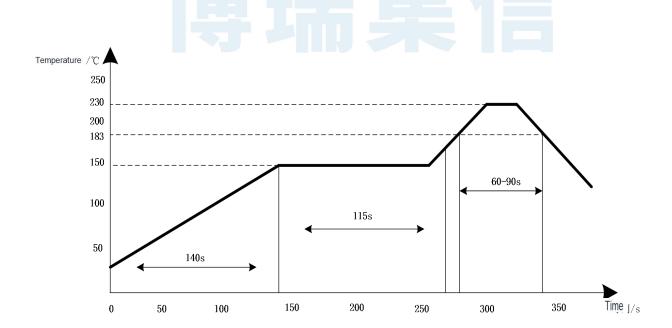

# **Recommended Soldering Temperature Profile**

V2.0.2

web: www.bonray.net